Suite à l'annonce récente de ses nouvelles puces Bonanza Mine, Intel est de retour avec une nouvelle puce bien adaptée à l'extraction de crypto-monnaie, ainsi qu'à l'amélioration des performances dans un large éventail d'applications telles que la virtualisation de réseau.

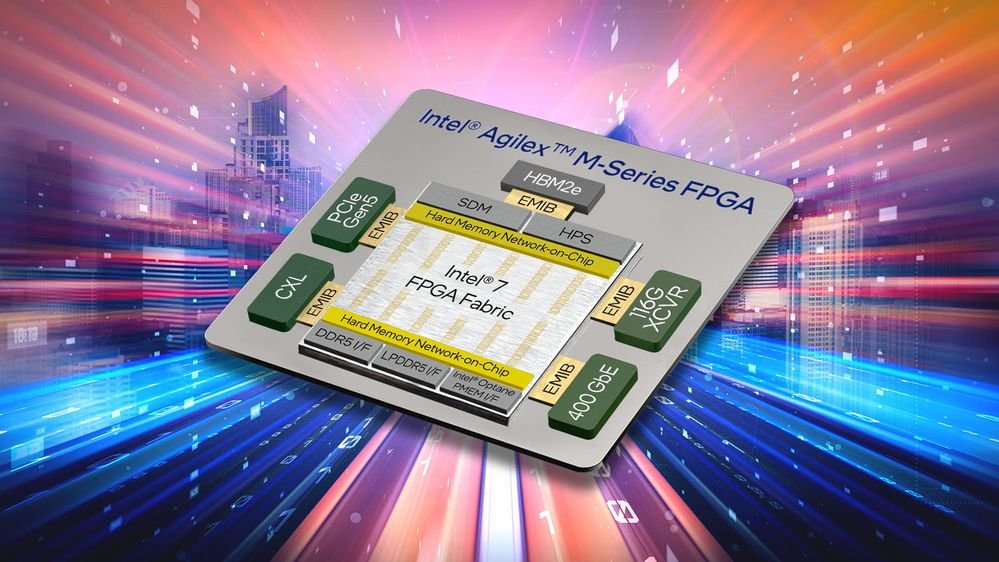

Le nouveau FPGA Agilex série M du géant des puces est basé sur la technologie de processus Intel 7 et vise à accélérer un large éventail de tâches, du calcul haute performance (HPC) au stockage et à la mise en réseau, selon une nouvelle version d'Intel. . En fait, bon nombre de ces applications sont gourmandes en mémoire, notamment en termes de capacité, de bande passante, de latence et d'efficacité énergétique.

Les FPGA Intel Agilex série M sont également les FPGA à bande passante mémoire la plus élevée du secteur avec une DRAM HBM intégrée. Cependant, cette nouvelle puce intègre plusieurs autres innovations et caractéristiques fonctionnelles pour améliorer la mise en réseau à haut débit, l'informatique et l'allocation de mémoire pour les applications réseau, cloud et embarquées.

En fait, Intel affirme que ses FPGA Agilex de la série M offrent également des performances de tissu par watt deux fois supérieures à celles des FPGA 7 nm concurrents, tels que le FPGA Xilinx Versal, dont la société mère appartient désormais à Intel AMD.

FPGA Intel Agilex série M

En plus d'être le premier membre de la famille d'appareils Intel Agilex à offrir la mémoire HMB2e, le nouveau FPGAS Agilex série M de la société comprend également des pilotes renforcés pour d'autres technologies de mémoire avancées telles que DDR4, DDR5 et LPDDR5.

Sabrina Gomex, directrice du marketing produit d'Intel, a fourni des informations supplémentaires dans un article de blog sur l'importance de la mémoire dans les nouveaux FPGA de l'entreprise, en disant :

« Tous les FPGA Intel Agilex, y compris les membres de la série M, incluent une SRAM rapide sur puce sous la forme de blocs MLAB et M20K. Ces mémoires SRAM sont intégrées dans la structure logique programmable du FPGA et sont donc situées immédiatement à côté de la logique qui va échanger des données avec ces mémoires. Certains FPGA Intel Agilex série M disposent également d'un HBM intégré sous la forme de piles de mémoire HBM2e, gérées par des contrôleurs de mémoire renforcés.

Les prochains FPGA Agilex série M d'Intel seront capables de gérer d'énormes charges de données, prenant en charge PCI Express Gen5, Compute Express Link, Ethernet 400G et des émetteurs-récepteurs série fonctionnant jusqu'à 116 Gbps.

Nous en entendrons probablement davantage de la part du fabricant de puces à l'approche de la sortie de ses nouveaux FPGA Agilex série M, espérons-le plus tard cette année.

Par le registre